-

I/O 아키텍처의 이해스토리지 지식 2020. 12. 23. 23:21

디스크 스토리지 시스템의 이해를 돕기 위해, IO 아키텍처와 BUS, 그리고 Disk Interface에 대해 알아본다.

I/O 아키텍처

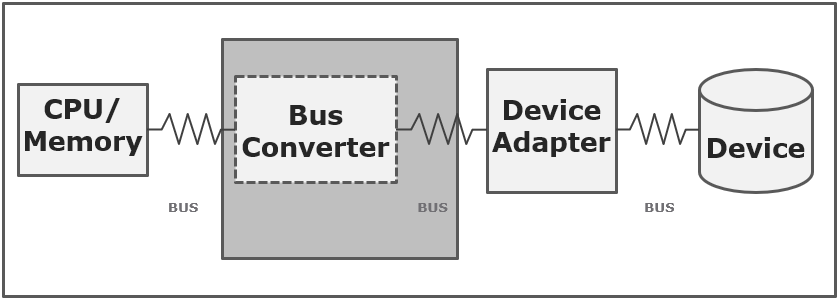

컴퓨터 시스템 내 여러 장치 간 데이터의 전송은 BUS를 통해 이루어진다. BUS는 쉽게, 데이터가 지나다니는 통로이다. 이는 기술의 발전에 따라 그 통로의 대역폭이 커지게 되어 한번에 보다 많은 양의 데이터를 전송할 수 있게 된다.

IO Architecture BUS의 변천

오랜 기간 컴퓨터 시스템의 성능 향상에 걸림돌이 되어 온 BUS의 병목이 PCIe의 등장으로 크게 해소된다.

BUS의 변천 Disk Interface

컴퓨터 시스템의 BUS에 Disk를 연결하기 위한 기술은 IDE 부터 SAS에 이르기까지 많은 발전을 거듭하였다.

Disk Interface Disk Interface 규격

- ATA (Advanced Technology Attachment)

- 컴퓨터 내부의 저장장치 연결을 위한 표준화된 인터페이스 - IDE/E-IDE (Enhanced Integrated Drive Electronics)

- 장치 컨트롤러가 드라이브 자체에 포함되어 있어 메인보드에는 어댑터만으로 인터페이스 추가

- 인터페이스 표준인 ATA를 컨트롤러 기술에 해당하는 IDE로 불리움

- E-IDE는 ATA 표준의 확장형으로서, 고용량의 드라이브 지원 - SATA (Serial Advanced Technology Attachment)

- ATA의 대안으로 고안되어 빠른 전송속도와 Hot plugging, 케이블 간소화, 안정성 강화

- 2010년 경부터 SCSI, ATA를 대체하고 주류가 된 접속 규격

- ATA의 단점인 병렬처리 시 대기시간을 줄이고 속도 향상을 위해 직렬처리 도입

- SATA는 컨트롤러를 내장하여 HDD와 CPU가 직접 통신하므로 HDD 수만큼 CPU에 부담이 됨

- SAS와의 인터페이스를 통합하여 서버시장까지 진출하여 빠른 성장과 안정성을 보임 - SCSI (Small Computer System Interface)

- 서버/워크스테이션 등에 쓰이는 고속 인터페이스

- PATA와 같이 병렬 전송 방식으로 발전하였고, PATA/SATA 대비 높은 안정성과 신뢰성 제공

- 병렬 전송의 한계에 부딪힘, 대역폭을 충분히 활용 가능한 고성능 SSD 등장으로 변화에 직면

- 스커지(scuzzy)로 발음 - SAS (Serial Attached SCSI)

- 기존 SCSI를 대체하는 진보된 디스크 인터페이스

- Ultra-320에서 Ultra-640으로 병렬SCSI 기술이 발전했으나 한계에 부딪힘

- 병렬 처리 문제를 해소한 SAS의 발표로 고속통신 가능

- SAS는 SCSI 컨트롤러가 CPU의 역할을 대신하여 모든 SAS HDD를 제어하므로 IO 부하 발생 시 SCSI 컨트롤러가 IO성능을 조정하여 CPU와 통신하므로 CPU 부하율이 줄어듦

- 채널당 8개의 디스크 연결 가능 (최대 65,535개)

디스크 인터페이스 규격 PCI와 PCIe

PCI & PCIe PCIe

- PCIe (Peripheral Component Interface Express)

- 병렬 방식 버스 아키텍처의 공통적인 한계점을 극복한 직렬 버스 아키텍처 (by INTEL)

- 하나의 회선을 공유하지 않고 두 개의 데이터 라인을 통해 송수신을 별도 처리 → 기존의 병목 제거

- 2.5GHz의 매우 높은 클럭으로 동작, 송수신 시 5Gbit/s 전송속도

- 8B10B encode 기법 적용으로 10bit 데이터 전송 시 에러 정정 코드 제외한 8bit만 데이터가 됨

- 즉, 2.5Gbit/8=312.5MB 아닌 2.5Gbit/10=250MB/s, 송수신 합하면 초당 500MB 대역폭을 가짐

- PCI Express x1/x2/x4/x8/x16/x32 복수의 링크 지원

- PCIe는 각 포트별 데이터 송수신 라인을 별도 사용하는 Serial 방식이므로 다수의 장치에서 데이터를 송수신하더라도 PCI에서의 지연과 병목 현상이 발생하지 않음

PCIe NVMe

- NVMe (Non-Volatile Memory Express)

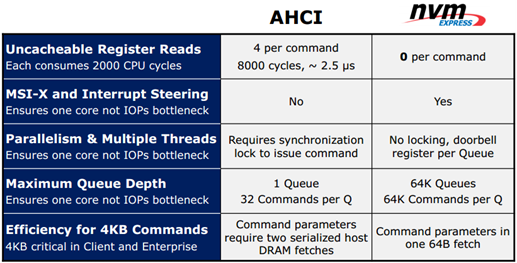

- AHCI보다 진화된 데이터 전송 기술 (프로토콜), 인텔 주도

- PCIe가 도로라면 NVMe는 SSD에 최적화된 신호등 체계

- AHCI는 하나의 컴맨드 완료에 9번의 레지스터 접근으로 지연시간 과다 → SSD 성능 소화 불가

- PCIe 기반 위에 컴맨드 처리 시 레지스터 접근을 2번으로 줄이는 새로운 구조로 지연 해소

- 다중 코어 프로세서 활용으로 대량의 컴맨드 처리 가능

정리하면, NVMe는 스토리지 장치를 위한 신호 규약이고, PCI Express 버스를 사용하는 SSD에만 적용된다. Command 처리시간이 짧아서 고속 데이터 전송과 대량의 데이터 요구를 동시에 처리 가능하다.

SCM

메인 메모리 (RAM)와 SSD의 성능 격차를 줄이기 위해 SCM (Storage Class Memory)이 등장하였다. 상대적으로 느린 SSD의 성능을 보완하기 위한 Caching 용도로 많이 사용한다.

Cache의 역할

Cache는 속도가 다른 장치/미디어 간 성능 손실을 완화하기 위해 범용 메모리를 사용하여 버퍼링 기능을 수행한다. SCM 역시 올플래시 스토리지의 성능을 더욱 향상시키기 위해 메인 메모리와 SSD 사이의 Caching을 담당하고 있다.

Cache의 역할 3D XPoint

- 3D XPoint?

- 인텔과 마이크론의 합작으로 탄생한 RAM과 플래시의 중간 형태의 비휘발성 메모리 기술

- 셀 위아래에 가로와 세로로 엇갈리는 금속 회로 교차점(크로스포인트)마다 0과 1의 신호를 담는 '메모리 셀'과 '메모리 셀렉터'를 설치

- 크로스 포인트마다 일종의 도로 주소를 지정해 정보를 한층 빨리 찾을 수 있도록 설계 - 장점

- NAND 플래시보다 속도, 내구성이 1000배, 집적도 10배 이상 (업체 주장)

- Low Latency : 100ns ~ 1us (cf. SSD 100us~1ms)

- Block 단위의 Erase 불필요 - 단점

- 내구성 및 수명 기대 이하

- 고비용 - 옵테인 (Optane)

- 최초로 크로스포인트 기술 탑재한 SSD 제품

- Latency : 10us

- Random Read 550,000, Write 500,000 IOPS - 발전 방향

- SSD 성능 최대화

- DRAM 대체하기 위한 SCM(Storage Class Memory) 용으로 사용

'스토리지 지식' 카테고리의 다른 글

VDI를 위한 스토리지 사이징 가이드 (0) 2020.12.28 VDI 데이터 절감율이 낮은 이유 (0) 2020.12.27 오라클 데이터 중복제거 안되는 이유 (0) 2020.12.26 데이터 압축 (Compression) (2) 2020.12.25 데이터 중복제거 (Deduplication) (0) 2020.12.24 - ATA (Advanced Technology Attachment)